### **PC SDRAM Specification**

**Revision 1.7**

November 1999

Order Number: Not Applicable

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE. Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

Copyright © Intel Corporation 1996, 1997, 1998, 1999

\*Third-party brands and names are the property of their respective owners.

# int<sub>e</sub>l<sub>®</sub> Contents

| 1.0 | Introdu                  | ction                                                                                                                                                                                                                                   | 1                    |

|-----|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|     | 1.1<br>1.2<br>1.3        | Objective<br>Scope of This Document<br>Convention Used                                                                                                                                                                                  | 1                    |

| 2.0 | Pinout                   | and Signal Description                                                                                                                                                                                                                  | 2                    |

|     | 2.1<br>2.2               | Device Pinouts<br>Signal Descriptions (Simplified)                                                                                                                                                                                      |                      |

| 3.0 | Basic F                  | Functional Description                                                                                                                                                                                                                  | 7                    |

|     | 3.1<br>3.2<br>3.3        | <ul> <li>Mode Register and the Modes Required to be supported</li> <li>Command Truth Table</li> <li>Address Bit Maps</li> <li>3.3.1 16M Address Bit Maps For Row And Column Addresses During Commands</li> </ul>                        | 8<br>14              |

|     |                          | 3.3.2 64M Address Bit Maps For Row And Column Addresses During Com-<br>mands                                                                                                                                                            | 15                   |

|     |                          | <ul> <li>3.3.3 128M Address Bit Maps For Row And Column Addresses During Com<br/>mands</li> <li>3.3.4 256M Address Bit Maps For Row And Column Addresses During Com<br/>mands</li> </ul>                                                | 16<br>I-             |

|     | 3.4                      | mands<br>Power-Up and Initialization Sequence<br>3.4.1 Power Up Sequence<br>3.4.2 Initialization Sequence                                                                                                                               | <b>17</b><br>17      |

|     | 3.5<br>3.6<br>3.7<br>3.8 | Precharge Selected Bank<br>Precharge All<br>NOP and Device Deselect<br>Row activate                                                                                                                                                     | 18<br>19<br>19       |

|     | 3.9<br>3.10<br>3.11      | Read Bank<br>Write Bank<br>Mode Register Set Command                                                                                                                                                                                    | 20                   |

| 4.0 | Essent                   | ial Functionality for the "PC SDRAM" Device                                                                                                                                                                                             |                      |

| 4.0 | 4.1<br>4.2               | Burst Read and Burst Write                                                                                                                                                                                                              | 22                   |

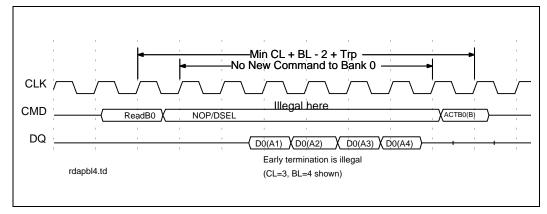

|     | 4.3<br>4.4               | Read and Write With AutoprechargePrecharge Termination of Burst4.4.1Precharge Command After a Burst Read4.4.2Precharge Termination of a Burst Read4.4.3Precharge Command After a Burst Write4.4.4Precharge Termination of a Burst Write | 24<br>24<br>25<br>26 |

|     | 4.5<br>4.6<br>4.7        | Read Terminated By Read<br>Write Terminated By Write<br>Read Terminated By Write                                                                                                                                                        | 26<br>27             |

|     | 4.8<br>4.9<br>4.10       | Write Terminated By Read<br>SDRAM Commands, To Two Or Four Banks, In Consecutive Clocks<br>Next Command To Same Bank After Precharge<br>4.10.1 Precharge Bank                                                                           | 28<br>29<br>29       |

|         | 4.10.2 Precharge All                                   |    |

|---------|--------------------------------------------------------|----|

|         | 4.10.3 Read-Auto_Precharge                             |    |

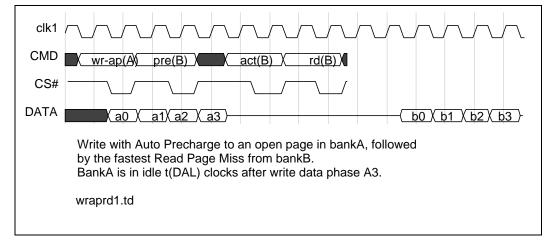

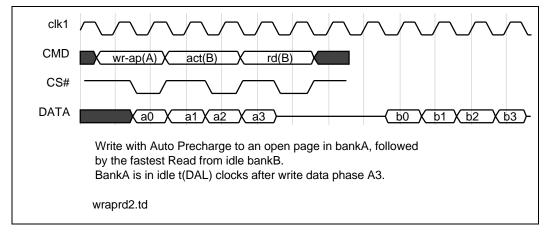

|         | 4.10.4 Write-Auto_Precharge                            |    |

| 4.11    | Concurrent Precharge Commands To Multiple Rows         | 29 |

| 4.12    | Back to back Command With Auto Precharge               |    |

| 4.13    | DQM# Latency                                           |    |

| 4.14    | Back to Back Command Support                           |    |

| 4.15    | Auto Refresh (CBR) Command                             |    |

| 4.16    | Self Refresh Entry/Exit                                |    |

| 4.17    | Low Power ICCLP                                        |    |

| 4.18    | Non-Required SDRAM Functionality                       |    |

| 4.19    | Multibank Operation                                    |    |

| Synchro | ronous DRAM AC/DC Parameters                           | 43 |

| 5.1     | DC Specifications                                      |    |

| 5.2     | A.C. Specifications                                    |    |

| 5.3     | IBIS: I/V Characteristics for Input and Output Buffers |    |

| 5.4     | IBIS Reference                                         |    |

| 5.5     | A.C. Timing Parameters                                 |    |

| 5.6     | Device Options                                         |    |

| 5.7     | Output Load Specification                              |    |

| 5.8     | Active Power in Application                            |    |

|         | •••                                                    |    |

### Figures

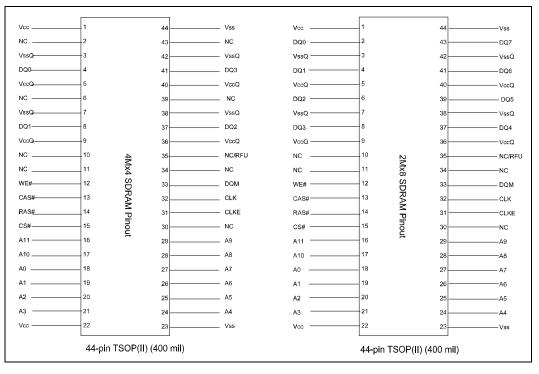

| 1  | Pin Assignment for 16M Devices (2Mx8, 4Mx4)                                | 2  |

|----|----------------------------------------------------------------------------|----|

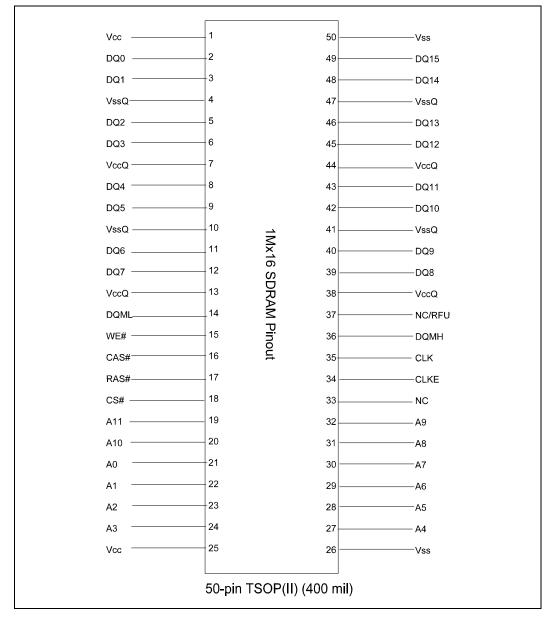

| 2  | Pin Assignment for 16M Device (1Mx16)                                      |    |

| 3  | Pin Assignment for 64M/128M Devices (16Mx4, 8Mx8, 4Mx16, 16Mx8, and 8Mx16) | 4  |

| 4  | Pin Assignment for 256M Devices (16Mx16, 32Mx8, and 64Mx4)                 |    |

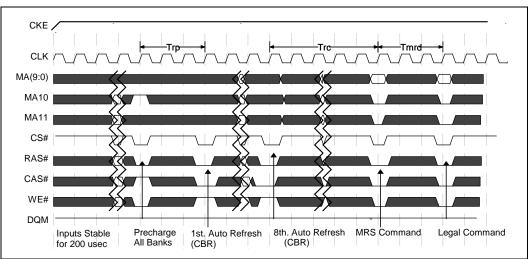

| 5  | Power Up Initialization Sequence                                           |    |

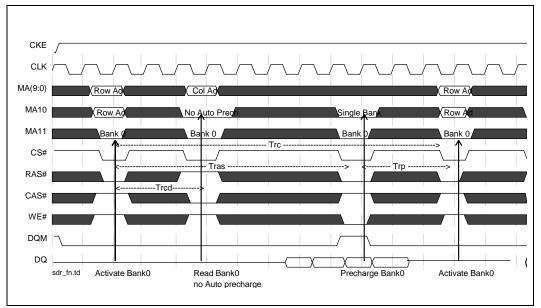

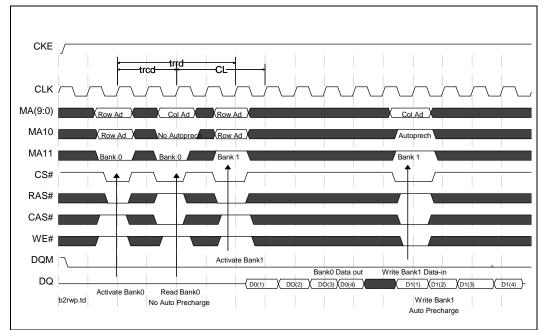

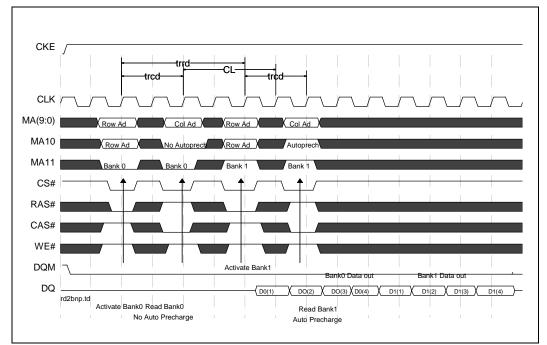

| 6  | Row Activate, Read and Precharge                                           |    |

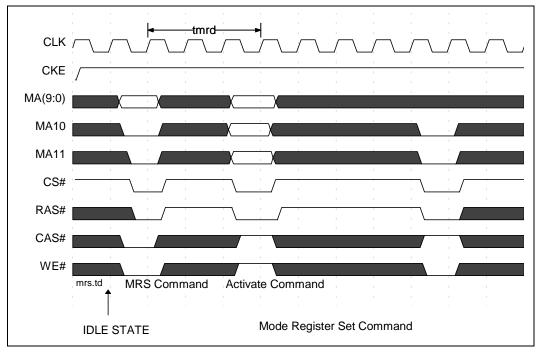

| 7  | Mode Register Set Command                                                  |    |

| 8  | Read and Write Commands (Burst Length 4 Shown)                             |    |

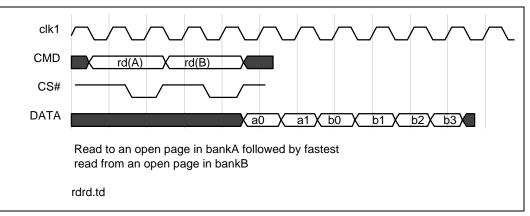

| 9  | Two Bank Ping Pong Read                                                    |    |

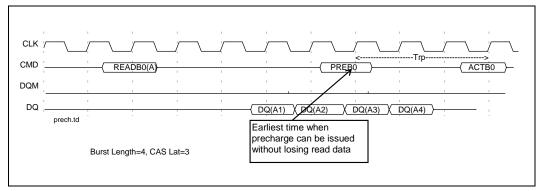

| 10 | Precharge Command After Burst Read                                         | 25 |

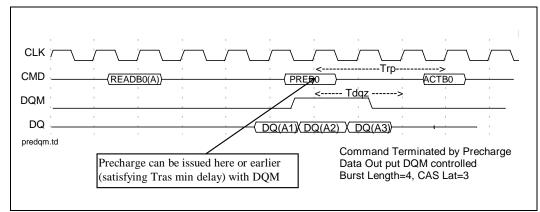

| 11 | Read Terminated by Precharge (Outputs DQM# Controlled)                     | 25 |

| 12 | Precharge Command after Burst Write                                        | 26 |

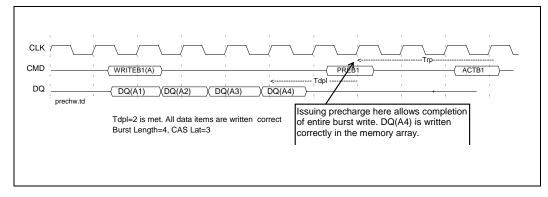

| 13 | Precharge Command After Write                                              | 26 |

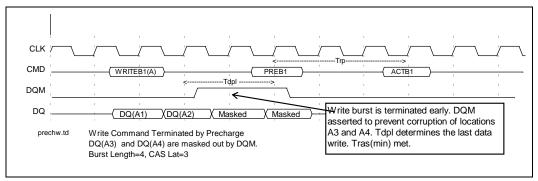

| 14 | Read Terminated By Read                                                    | 27 |

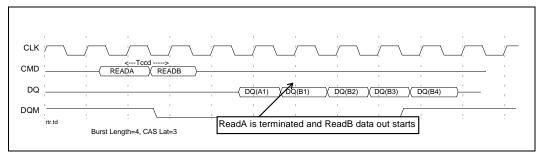

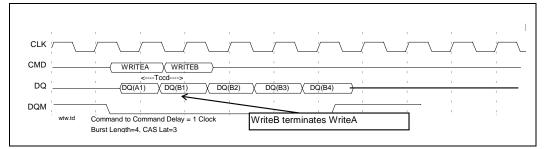

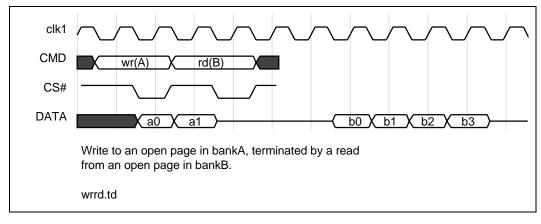

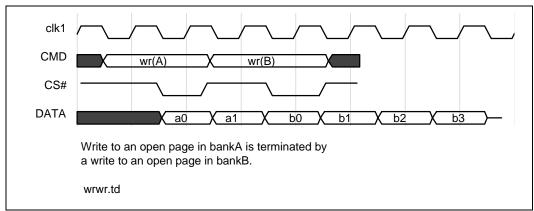

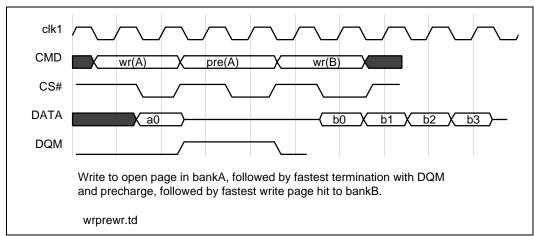

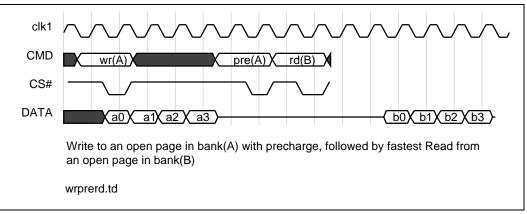

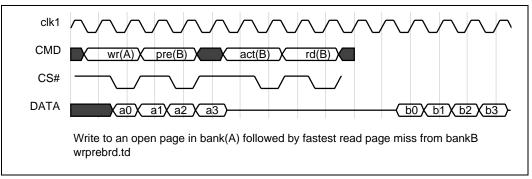

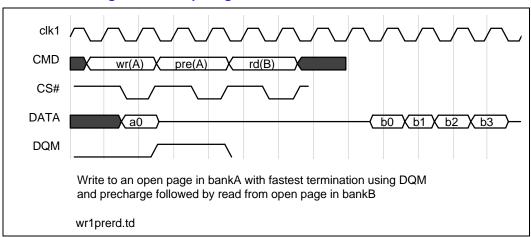

| 15 | Write Terminated with Write                                                |    |

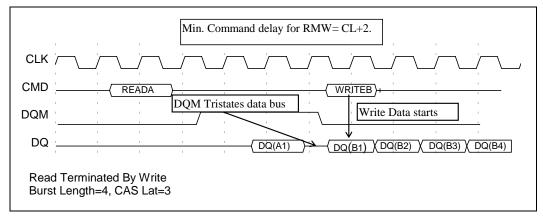

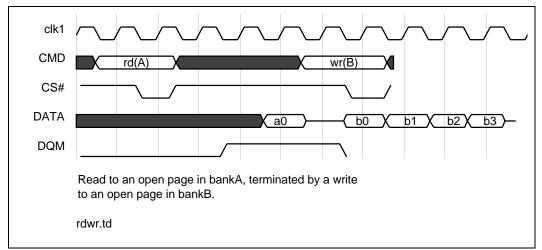

| 16 | Read Terminated By Write                                                   | 28 |

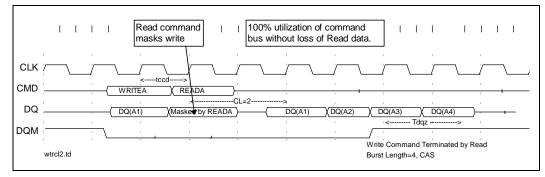

| 17 | Write terminated by Read (CL=2)                                            | 28 |

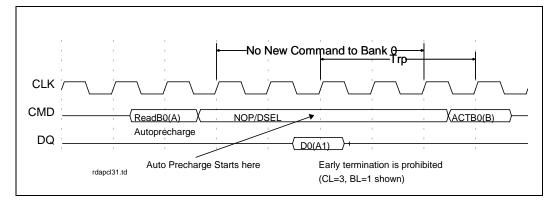

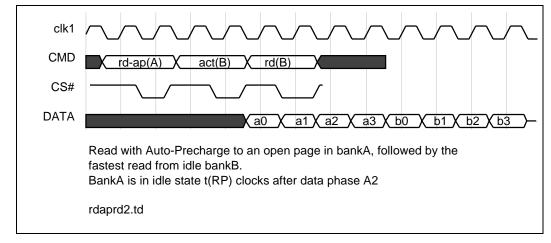

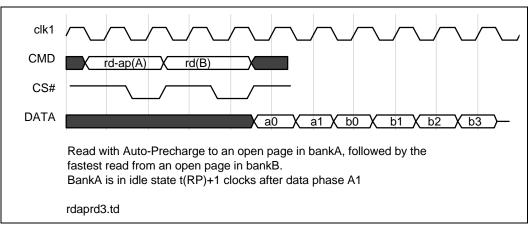

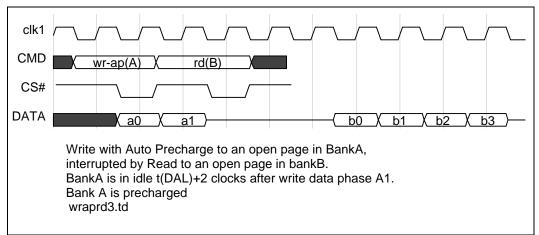

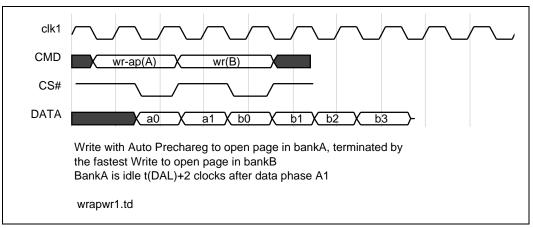

| 18 | Read Command with Auto Precharge (BL=4)                                    | 30 |

| 19 | Read Command with Auto Precharge (BL=1)                                    | 30 |

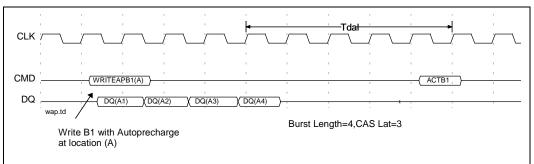

| 20 | Write Command With Autoprecharge (BL=4)                                    |    |

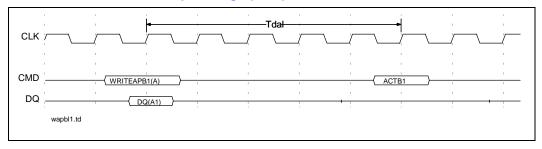

| 21 | Write Command With Autoprecharge (Bl=1)                                    |    |

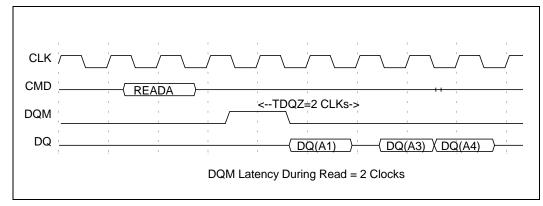

| 22 | DQM# Latency, Read Cycle                                                   | 32 |

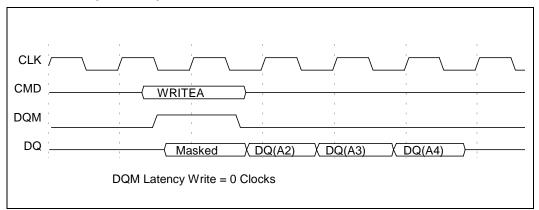

| 23 | DQM# Latency, Write Cycle                                                  | 32 |

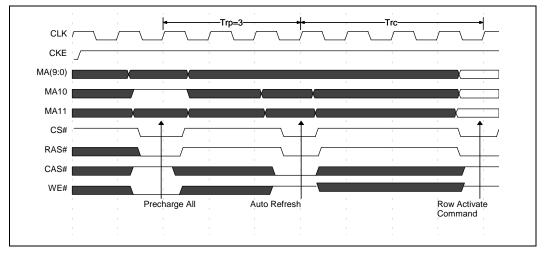

| 24 | Auto Refresh and Precharge All Command                                     |    |

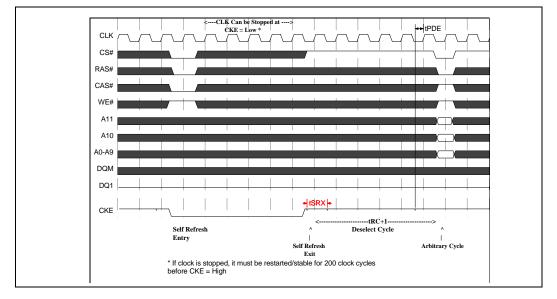

| 25 | Self Refresh Entry and Exit                                                |    |

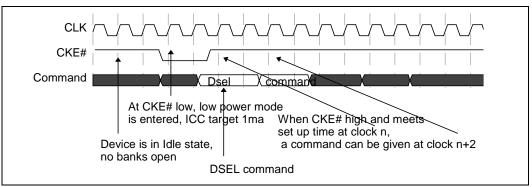

| 26 | Low Power ICCLP                                                            | 34 |

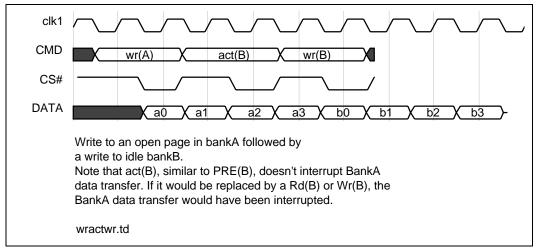

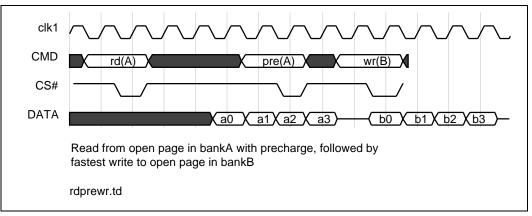

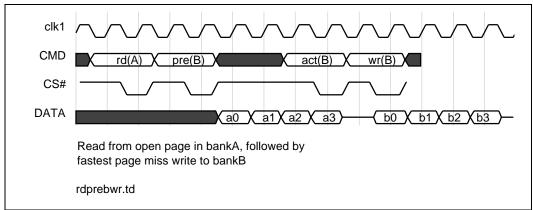

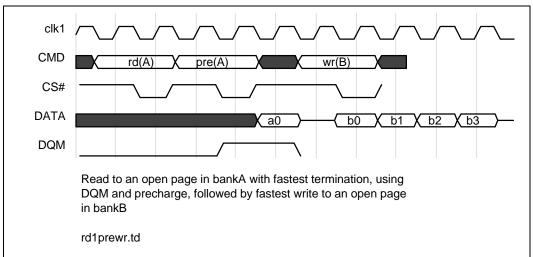

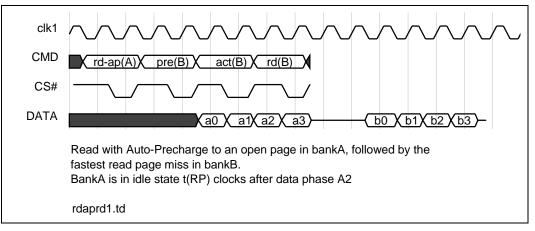

| 27 | Multibank Timing Relationship Diagram A                                    | 35 |

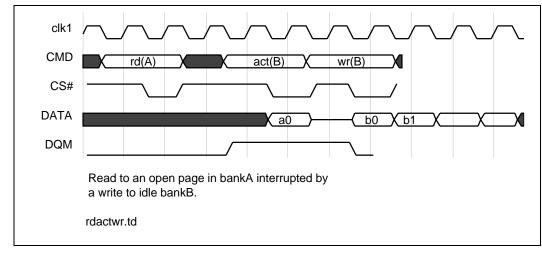

| 28 | Multibank Timing Relationship Diagram B                                    |    |

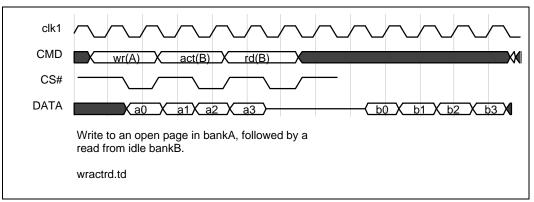

| 29 | Multibank Timing Relationship Diagram C                                    |    |

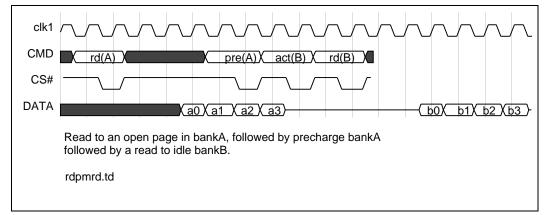

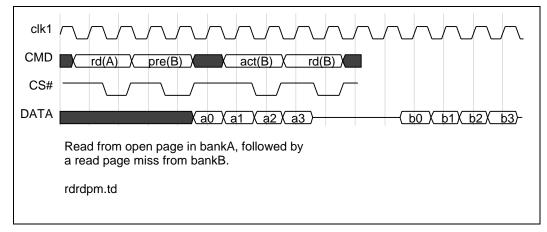

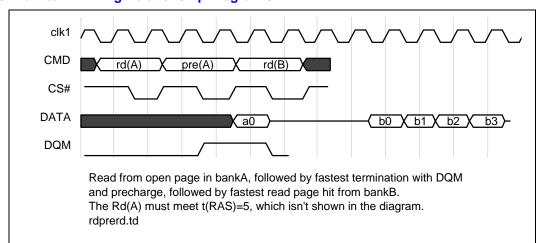

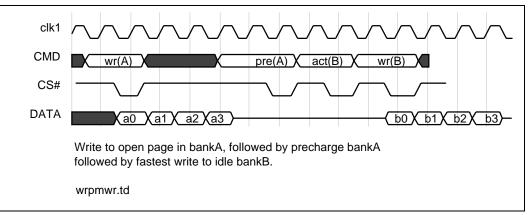

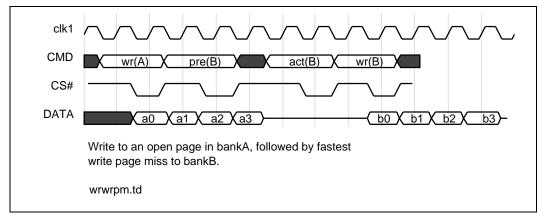

| 30 | Multibank Timing Relationship Diagram D                                    |    |

| 31 | Multibank Timing Relationship Diagram E                                    |    |

| 32 | Multibank Timing Relationship Diagram F                                    |    |

| 33 | Multibank Timing Relationship Diagram G                                    |    |

| 34 | Multibank Timing Relationship Diagram H                                    |    |

| 35 | Multibank Timing Relationship Diagram I                                    |    |

| 36 | Multibank Timing Relationship Diagram J                                    |    |

| 37 | Multibank Timing Relationship Diagram K                                    |    |

| 38 | Multibank Timing Relationship Diagram L                                    |    |

| 39 | Multibank Timing Relationship Diagram M                                    |    |

| 40 | Multibank Timing Relationship Diagram N                                    |    |

| 41 | Multibank Timing Relationship Diagram O                                    |    |

| 42 | Multibank Timing Relationship Diagram P                                    |    |

| 43 | Multibank Timing Relationship Diagram Q                                    |    |

| 44 | Multibank Timing Relationship Diagram R                                    |    |

| 45 | Multibank Timing Relationship Diagram S                                    |    |

| 46 | Multibank Timing Relationship Diagram T                                    |    |

| 47 | Multibank Timing Relationship Diagram U                                    |    |

| 48 | Multibank Timing Relationship Diagram V                                    | 42 |

| 49 | Multibank Timing Relationship Diagram W                                 | 42 |

|----|-------------------------------------------------------------------------|----|

| 50 | Multibank Timing Relationship Diagram X                                 | 42 |

| 51 | Multibank Timing Relationship Diagram Y                                 | 43 |

| 52 | Multibank Timing Relationship Diagram Z                                 | 43 |

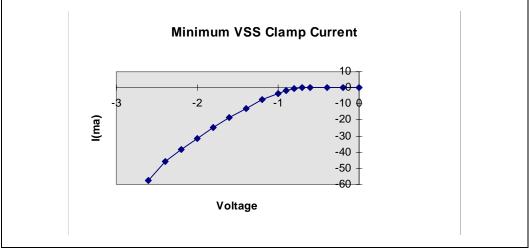

| 53 | SDRAM VSS Clamp Characteristics                                         | 47 |

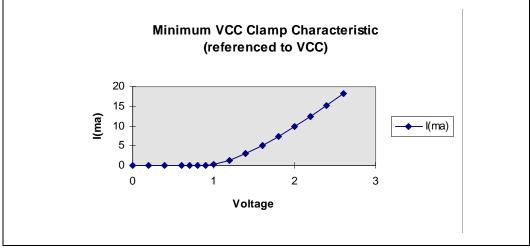

| 54 | SDRAM VCC Clamp Characteristics                                         | 48 |

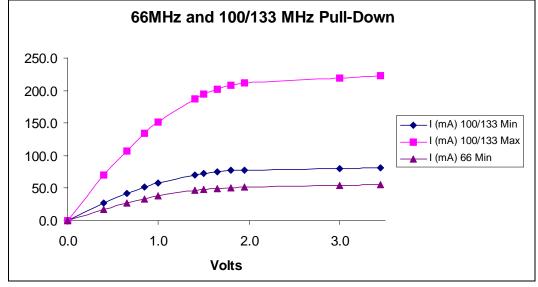

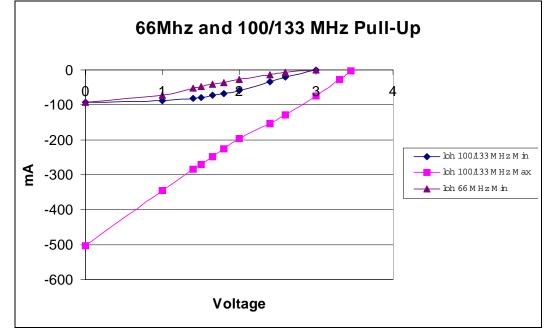

| 55 | SDRAM DQ Output Buffer Pull-Down Characteristics                        | 49 |

| 56 | SDRAM DQ Output Buffer Pull-Up Characteristics (For VCC = 3.0v - 3.45v) | 50 |

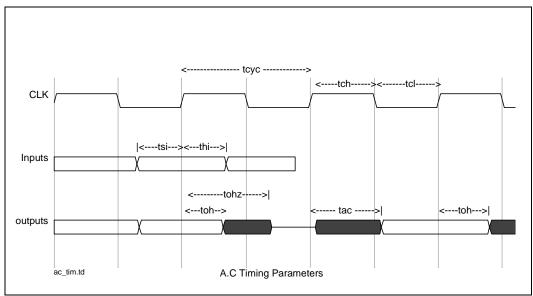

| 57 | A.C Timing Parameters                                                   | 54 |

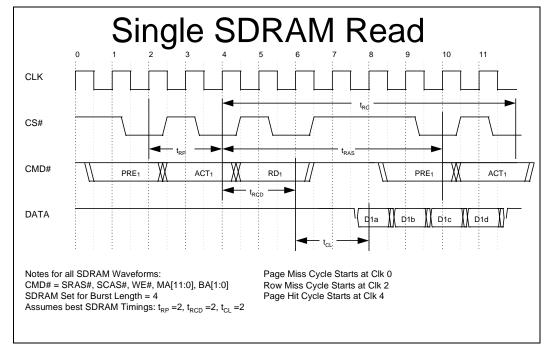

| 58 | Read Cycle with timing                                                  | 55 |

| 59 | Write Cycle with timing                                                 |    |

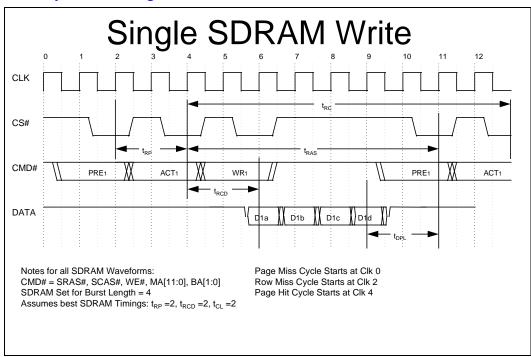

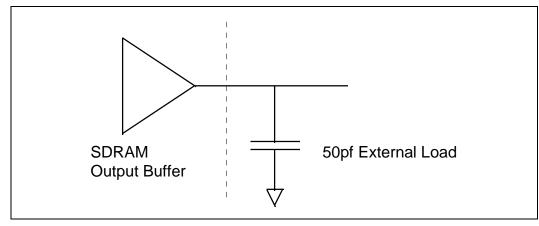

| 60 | Output Load Circuit                                                     | 56 |

|    |                                                                         |    |

#### **Tables**

| 1  | Pin Functional Description (16M bit devices)                                      | . 6 |

|----|-----------------------------------------------------------------------------------|-----|

| 2  | Latency Mode (LT Field)                                                           | . 7 |

| 3  | Wrap Type (WT Field)                                                              | . 7 |

| 4  | Burst Length (BL Field)                                                           | . 7 |

| 5  | Burst Address Ordering for Burst Length (BL=1,2,4)                                | . 7 |

| 6  | Command Truth Table                                                               | . 8 |

| 7  | DQM# Truth Table                                                                  | . 9 |

| 8  | Operative Command Table                                                           | . 9 |

| 9  | Row/Column Addresssing Per Memory Size/# Banks                                    | 13  |

| 10 | Row Address Table (ACT, PRE)                                                      | 14  |

| 11 | Column Address Table (Read/Write/Read AP/Write AP)                                | 14  |

| 12 | Row Address Table (ACT, PRE) (per JEDEC Standard)                                 | 15  |

| 13 | Column Address Table (Read/Write/Read AP/Write AP)                                | 15  |

| 14 | Row Address Table (ACT, PRE)                                                      |     |

| 15 | Column Address Table (Read/Write/Read AP/Write AP)                                | 16  |

| 16 | Row Address Table (ACT, PRE)                                                      | 17  |

| 17 | Column Address Table (Read/Write/Read AP/Write AP)                                | 17  |

| 18 | Partial list of Timing Paramters for Multibank Timing Relationship Diagrams (Figu |     |

|    | 27 to Figure 51)                                                                  |     |

| 19 | Absolute Maximum D.C. Rating                                                      |     |

| 20 | D.C Operating Requirements                                                        |     |

| 21 | Maximum AC Operating Requirements                                                 |     |

| 22 | Refresh Rate                                                                      |     |

| 23 | SDRAM DQ Buffer Output Drive Characteristics                                      |     |

| 24 | Data Points For Figure 53                                                         |     |

| 25 | Data Points For Figure 54                                                         |     |

| 26 | Data Points For Figure 55                                                         | 49  |

| 27 | Data Points For Figure 56                                                         | 50  |

| 28 | 133/100/66 MHz AC Timing Parameters For CL=2 and 3                                |     |

| 29 | Matrix for 66 MHz Devices and The Target for 100/133 MHz Devices                  | 54  |

|    |                                                                                   |     |

#### **Revision History**

| Rev. | Description                                                                                          |

|------|------------------------------------------------------------------------------------------------------|

|      | <ul> <li>Add AC timing specifications for 133MHz SDRAM</li> </ul>                                    |

|      | • Update DC characteristics including current and capacitance specifications for 133MHz SDRAM        |

| 1.7  | • Add address bit map tables for 128M 4 banks and 256M 4 banks                                       |

| 1.7  | • Update Table 29 to include 133MHz devices in the matrix                                            |

|      | • Update Section 5.8 to include 3 DIMM, 133MHz in the calculation of power in application            |

|      | • Miscellaneous changes for consistency                                                              |

| 1.63 | Document Re-formatting. No specification content changes                                             |

| 1.62 | Add 7.8usec refresh rate for 256M Devices                                                            |

|      | Add 256M Pinout                                                                                      |

| 1.61 | • Add 64Mx4 Addressing definition                                                                    |

| 1.01 | Remove 64M 2 bank addressing definition                                                              |

|      | • Added: Clock will stabilize within 100usec before 1 <sup>st</sup> command to SDRAM                 |

|      | Add 256M bit addressing                                                                              |

| 1.6  | Set 64M 4 Bank Precharge Table, A11=A12, A12=A13                                                     |

|      | <ul> <li>Set Troh=CL as max value , not min</li> <li>Clarify Tambient operation conditons</li> </ul> |

|      | Corrected 64M/128 Pin out Pin45/46                                                                   |

|      | • Iccslfrf current changed to 1ma                                                                    |

|      | • Cin to be measured at 23C, 1Mhz, 1.4v bias, 200mv swing, Vcc = 3.3v                                |

| 1.51 | • Trise/Tfall times to be characterized into 50pf, values given                                      |

|      | • Changed Vin/Vout max from VDD+0.5V to 4.5V                                                         |

|      | • Changed tohz max (66Mhz) from 9ns to 12ns                                                          |

|      | • 128M bit Pin out (54pin TSOP)                                                                      |

|      | • 128M bit Addressing Support                                                                        |

|      | • Change Power Up Sequence, only CS# needs to be inactive                                            |

| 1.5  | • Add Tohz, Output valid to Z Time                                                                   |

|      | Add Output Load Section                                                                              |

|      | Active Power Discussion                                                                              |

#### 1.0 Introduction

#### 1.1 Objective

The objective of this document is to define a new Synchronous DRAM specification ("PC SDRAM") which will remove extra functionality from the current JEDEC standard SDRAM specification, so that it will be a "fully compatible" device among all vendor designed parts. It should be easy to design and manufacture and highly cost optimized for the main stream volume desktop Intel architecture PCs.

#### 1.2 Scope of This Document

The scope of this document is limited to identify and define all the essential functionality that is needed to be implemented for the first generation "PC SDRAM". Implementation details are left to the designers of the device.

#### 1.3 Convention Used

The following lists some of the nomenclature conventions used in this document:

- The "#" sign at the end of a signal name indicates active low signals (e.g., CS#, RAS#, etc).

- "B0" or "B1" at the end of a command name indicates the bank (e.g., READB0 indicates the READ Command for Bank 0; READB1 indicates the READ Command for Bank 0).

- "(A)" indicates the start address for the associated command (e.g., READB0(A)).

- "WRITEA" indicates a Write at an address starting at location (A); Either Bank

- "DQ(A1)" indicates the 1<sup>st</sup> data item for the access starting at location (A).

#### 2.0 Pinout and Signal Description

#### 2.1 Device Pinouts

The pinout for different SDRAM configurations are shown in this section.

#### Figure 1. Pin Assignment for 16M Devices (2Mx8, 4Mx4)

#### Figure 2. Pin Assignment for 16M Device (1Mx16)

| Figure 3. | Pin Assignment for | 64M/128M Devices | (16Mx4, 8Mx8, | 4Mx16, 16Mx8 | , and 8Mx16) |

|-----------|--------------------|------------------|---------------|--------------|--------------|

|           |                    |                  |               |              |              |

|                                                                                                                                                                                                                             |                                                                                                                                                                                                      |                                                                                                                                                                                                                     | _                                                                                                                                                               | 4M x 16 /<br>8M x8 / 1<br>16M x 4 |                                                                                                                                                                |                                                                                                                                                                                        |                                                                                                                                                                                                |                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC<br>DQ0<br>VCCQ<br>DQ1<br>DQ2<br>VSSQ<br>DQ3<br>DQ4<br>VCCQ<br>DQ5<br>DQ6<br>VSSQ<br>DQ7<br>VCC<br>DQML<br>WE#<br>CAS#<br>RAS#<br>CAS#<br>RAS#<br>CAS#<br>A13(BA0)<br>A12(BA1)<br>A10(AP)<br>A0<br>A1<br>A2<br>A3<br>VCC | VCC<br>DQ0<br>VCCQ<br>NC<br>DQ1<br>VSSQ<br>NC<br>DQ2<br>VCCQ<br>NC<br>DQ3<br>VSSQ<br>NC<br>VCC<br>NC<br>WE#<br>CAS#<br>RAS#<br>CS#<br>A13(BA0)<br>A12(BA1)<br>A10(AP)<br>A0<br>A1<br>A2<br>A3<br>VCC | VCC<br>NC<br>VCCQ<br>NC<br>DQ0<br>VSSQ<br>NC<br>VCCQ<br>NC<br>VCCQ<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>WE#<br>CAS#<br>RAS#<br>CAS#<br>RAS#<br>CAS#<br>A13(BA0)<br>A12(BA1)<br>A10(AP)<br>A0<br>A1<br>A2<br>A3<br>VCC | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>0<br>21<br>22<br>3<br>24<br>25<br>26<br>27<br>54 | d<br>U<br>L<br>C<br>C<br>C        | 54<br>53<br>52<br>51<br>50<br>49<br>48<br>47<br>46<br>45<br>44<br>43<br>42<br>41<br>40<br>39<br>38<br>37<br>36<br>35<br>34<br>33<br>32<br>31<br>30<br>29<br>28 | VSS<br>NC<br>VSSQ<br>NC<br>DQ3<br>VCCQ<br>NC<br>VSSQ<br>NC<br>DQ2<br>VCCQ<br>NC<br>VSS<br>RESERVED<br>DQM<br>CLK<br>CLKE<br>RESERVED<br>A11<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>VSS | VSS<br>DQ7<br>VSSQ<br>NC<br>DQ6<br>VCCQ<br>NC<br>DQ5<br>VSSQ<br>NC<br>DQ4<br>VCCQ<br>NC<br>VSS<br>RESERVED<br>DQM<br>CLK<br>CLKE<br>RESERVED<br>A11<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>VSS | VSS<br>DQ15<br>VSSQ<br>DQ14<br>DQ13<br>VCCQ<br>DQ12<br>DQ11<br>VSSQ<br>DQ10<br>DQ9<br>VCCQ<br>DQ8<br>VSS<br>RESERVED<br>DQMH<br>CLK<br>CLKE<br>RESERVED<br>DQMH<br>CLK<br>CLKE<br>RESERVED<br>A11<br>A9<br>A8<br>A7<br>A6<br>A5<br>AA4<br>VSS |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16Mx16<br>32M x 8<br>64M x 4                           |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                   |                                                                                                                                                                                           |                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC<br>DQ0<br>VCCQ<br>DQ1<br>DQ2<br>VSSQ<br>DQ3<br>DQ4<br>VCCQ<br>DQ5<br>DQ6<br>VSSQ<br>DQ7<br>VCC<br>DQML<br>WE#<br>CAS#<br>RAS#<br>CS#<br>A13(BA0)<br>A12(BA1)<br>A10(AP)<br>A0<br>A1<br>A2<br>A3<br>VCC | VCC<br>DQ0<br>VCCQ<br>NC<br>DQ1<br>VSSQ<br>NC<br>DQ2<br>VCCQ<br>NC<br>DQ3<br>VSSQ<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>WE#<br>CAS#<br>RAS#<br>CS#<br>A13(BA0)<br>A12(BA1)<br>A10(AP)<br>A0<br>A1<br>A2<br>A3<br>VCC | VCC<br>NC<br>VCCQ<br>NC<br>DQ0<br>VSSQ<br>NC<br>VCCQ<br>NC<br>VCCQ<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>VCC<br>NC<br>VCCQ<br>NC<br>VCCQ<br>NC<br>DQ1<br>VSSQ<br>NC<br>NC<br>VCCQ<br>NC<br>DQ1<br>VSSQ<br>NC<br>NC<br>VCCQ<br>NC<br>DQ1<br>VSSQ<br>NC<br>NC<br>VCCQ<br>NC<br>DQ1<br>VSSQ<br>NC<br>NC<br>VCCQ<br>NC<br>DQ1<br>VSSQ<br>NC<br>NC<br>VCCQ<br>NC<br>DQ1<br>VSSQ<br>NC<br>NC<br>VCCQ<br>NC<br>DQ1<br>VSSQ<br>NC<br>NC<br>VCCQ<br>NC<br>DQ1<br>VSSQ<br>NC<br>VCCQ<br>NC<br>DQ1<br>VSSQ<br>NC<br>VCCQ<br>NC<br>DQ1<br>VSSQ<br>NC<br>VCCQ<br>NC<br>VCCQ<br>NC<br>VCCQ<br>NC<br>VCCQ<br>NC<br>VCCQ<br>NC<br>VCCQ<br>NC<br>VCCQ<br>NC<br>VCCQ<br>NC<br>VCCQ<br>NC<br>VCCQ<br>NC<br>VCC<br>VCC<br>NC<br>VCC<br>NC<br>VCC<br>VCCQ<br>NC<br>VCC<br>VCCQ<br>NC<br>VCC<br>VCC<br>NC<br>VCC<br>NC<br>VCC<br>VCCQ<br>NC<br>VCC<br>VCC<br>VCC<br>NC<br>VCC<br>VCC<br>VCC<br>VCC<br>VCC<br>V | 1 2 3 4 5 6 7 8 9 10 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | <ul> <li>54</li> <li>53</li> <li>52</li> <li>51</li> <li>50</li> <li>49</li> <li>48</li> <li>47</li> <li>46</li> <li>45</li> <li>44</li> <li>43</li> <li>42</li> <li>41</li> <li>40</li> <li>39</li> <li>38</li> <li>37</li> <li>36</li> <li>35</li> <li>34</li> <li>33</li> <li>32</li> <li>31</li> <li>30</li> <li>29</li> <li>28</li> </ul> | VSS<br>NC<br>VSSQ<br>NC<br>DQ3<br>VCCQ<br>NC<br>VSSQ<br>NC<br>DQ2<br>VCCQ<br>NC<br>VSS<br>RESERVED<br>DQM<br>CLK<br>CLKE<br>A14<br>A11<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>VSS | VSS<br>DQ7<br>VSSQ<br>NC<br>DQ6<br>VCCQ<br>NC<br>DQ5<br>VSSQ<br>NC<br>DQ4<br>VCCQ<br>NC<br>VSS<br>RESERVED<br>DQM<br>CLK<br>CLKE<br>A14<br>A11<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>VSS | VSS<br>DQ15<br>VSSQ<br>DQ14<br>DQ13<br>VCCQ<br>DQ12<br>DQ11<br>VSSQ<br>DQ10<br>DQ9<br>VCCQ<br>DQ8<br>VSS<br>RESERVED<br>DQMH<br>CLK<br>CLKE<br>A14<br>A11<br>A9<br>A8<br>A7<br>A6<br>A5<br>AA4<br>VSS |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 54-pin TS                                              | SOP(I                                                                                                                                                                                                                                                                                                                                          | II)                                                                                                                                                                               |                                                                                                                                                                                           |                                                                                                                                                                                                       |

#### Figure 4. Pin Assignment for 256M Devices (16Mx16, 32Mx8, and 64Mx4)

#### 2.2 Signal Descriptions (Simplified)

#### Table 1. Pin Functional Description (16M bit devices)

| Symbol       | Туре                                      | Description <sup>1</sup>                                                                                                                                                                        |

|--------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[n:0]       | Input - Synchronous                       | Some address pin definitions change as a function of array size and # of banks used.                                                                                                            |

| CLK          | Input - Clock                             | Master Clock input.                                                                                                                                                                             |

| CKE          | Input - Clock Enable                      | Activates the CLK signal when high and deactivates when low. By deactivating the clock, CLKE low intitates the Power Down mode, Self Refresh mode or Suspend Mode.                              |

| RAS#         | Input - Synchronous                       | Row address strobe.                                                                                                                                                                             |

| CS#          | Input - Synchronous                       | Selects chip when active.                                                                                                                                                                       |

| CAS#         | Input - Synchronous                       | Column address strobe.                                                                                                                                                                          |

| WE#          | Input - Synchronous                       | Write Enable strobe.                                                                                                                                                                            |

| DQM#,DQML/H# | Input - Synchronous                       | DQ Mask. Active high. Controls the data output buffers in read<br>mode.<br>In write mode it masks the data from being written to the memory<br>array.                                           |

| DQ(x:0)      | Input/Output -<br>Synchronous             | Data IO pins.                                                                                                                                                                                   |

| NC/RFU       | No connect/<br>Reserved for Future<br>Use | This pin should be left No Connect on the device so that the normal functionality of the device is not be affected by the external connection to this pin.<br>This pin could be used in future. |

| Vcc, Vss     | Power pins                                | Supply Pins for the core                                                                                                                                                                        |

| VccQ, VssQ   | Power pins                                | Supply Pins for the output buffers                                                                                                                                                              |

#### NOTES:

1. See the Truth Table and functional description for detailed information about the functionality.

#### 3.0 Basic Functional Description

#### 3.1 Mode Register and the Modes Required to be supported

Mode Register Set: (Programming mode)

| 11 | 10 | 9 | 8 | 7 | 6      | 4 | 3  | 2  | 0 |

|----|----|---|---|---|--------|---|----|----|---|

| 0  | 0  | 0 | 0 | 0 | LTMODE |   | WT | BL |   |

#### Table 2. Latency Mode (LT Field)

| Bits (654) | CAS# Latency |

|------------|--------------|

| 010        | 2            |

| 011        | 3            |

| All Other  | reserved     |

#### Table 3. Wrap Type (WT Field)

| Bit 3 | Туре       |

|-------|------------|

| 0     | Linear     |

| 1     | Interleave |

#### Table 4. Burst Length (BL Field)

| Bits (210) | Burst Length |

|------------|--------------|

| 000        | 1            |

| 001        | 2            |

| 010        | 4            |

| All Other  | reserved     |

#### Table 5. Burst Address Ordering for Burst Length (BL=1,2,4)

| Burst Length | Starting Bit | Interleave | Linear  |

|--------------|--------------|------------|---------|

| 2            | 0            | 0,1        | 0,1     |

| 2            | 1            | 1,0        | 1,0     |

| 4            | 00           | 0,1,2,3    | 0,1,2,3 |

| 4            | 01           | 1,0,3,2    | 1,2,3,0 |

| 4            | 10           | 2,3,0,1    | 2,3,0,1 |

| 4            | 11           | 3,2,1,0    | 3,0,1,2 |

#### 3.2 Command Truth Table

#### Table 6. Command Truth Table

| Function                           | Symbol  | CKE<br>n-1 | CKE<br>n | CS# | RAS# | CAS# | WE# | A11 | A10 | BA(0:1) | A9-A0 |

|------------------------------------|---------|------------|----------|-----|------|------|-----|-----|-----|---------|-------|

| Device<br>deselect                 | DSEL    | Н          | х        | Н   | Х    | Х    | Х   | х   | х   | х       | Х     |

| No<br>Operation                    | NOP     | Н          | х        | L   | Н    | Н    | Н   | х   | х   | х       | Х     |

| Read                               | READ    | Н          | Х        | L   | Н    | L    | Н   | V   | L   | V       | V     |

| Read w/ auto<br>precharge          | READAP  | Н          | х        | L   | Н    | L    | Н   | V   | н   | V       | V     |

| Write                              | WRIT    | Н          | Х        | L   | Н    | L    | L   | V   | L   | V       | V     |

| Write w/<br>auto<br>precharge      | WRITEAP | Н          | х        | L   | Н    | L    | L   | v   | н   | V       | V     |

| Bank<br>Activate                   | ACT     | Н          | х        | L   | L    | Н    | Н   | V   | V   | V       | V     |

| Precharge select bank              | PRE     | Н          | х        | L   | L    | Н    | L   | V   | L   | V       | Х     |

| Precharge all banks                | PALL    | Н          | х        | L   | L    | Н    | L   | х   | н   | х       | Х     |

| Auto refresh                       | CBR     | Н          | Н        | L   | L    | L    | Н   | Х   | Х   | Х       | Х     |

| Self refresh<br>entry from<br>IDLE | SLFRSH  | Н          | L        | L   | L    | L    | Н   | x   | x   | х       | х     |

| Self refresh<br>exit               | SLFRSHX | L          | н        | Н   | Х    | Х    | Х   | х   | х   | х       | Х     |

| Power<br>Down entry<br>from IDLE   | PWRDN   | Н          | L        | х   | х    | х    | х   | x   | x   | х       | х     |

| Power<br>Down exit                 | PWRDNX  | L          | н        | Н   | Х    | Х    | Х   | х   | х   | х       | Х     |

| Mode<br>register set               | MRS     | Н          | х        | L   | L    | L    | L   | L   | L   | V       | V     |

NOTES:

1. H: High Level, L: Low Level, X: don't care, V: Valid data input

#### PC SDRAM Specification

# intel®

#### Table 7. DQM# Truth Table

| Function                                | CKE<br>n-1 | CKE<br>n | DQM#<br>U | DQM#<br>L |

|-----------------------------------------|------------|----------|-----------|-----------|

| Data write/output enable                | н          | Х        | L         | L         |

| Data mask/output disable                | н          | Х        | Н         | Н         |

| Upper byte write enable/lower byte mask | н          | Х        | L         | н         |

| Lower byte write enable/high byte mask  | н          | Х        | Н         | L         |

#### NOTES:

1. H: High Level, L: Low Level, X: don't care

#### Table 8. Operative Command Table (Sheet 1 of 4)

| Current<br>state | CS# | RAS# | CAS# | WE# | Address   | Command      | Action                                 | Notes |

|------------------|-----|------|------|-----|-----------|--------------|----------------------------------------|-------|

| Idle             | н   | х    | х    | х   | Х         | DSEL         | Nop or Power<br>Down                   | 3     |

|                  | L   | н    | Н    | н   | Х         | NOP          | Nop or Power<br>Down                   | 3     |

|                  | L   | Н    | L    | Н   | BA,CA,A10 | READ/READAP  | ILLEGAL                                | 4     |

|                  | L   | Н    | L    | L   | BA,CA,A10 | WRIT/WRITEAP | ILLEGAL                                | 4     |

|                  | L   | L    | Н    | н   | BA,RA     | ACT          | Row Active                             |       |

|                  | L   | L    | Н    | L   | BA,A10    | PRE/PALL     | NOP                                    |       |

|                  | L   | L    | L    | н   | Х         | CBR/SELF     | Refresh or Self refresh                | 5     |

|                  | L   | L    | L    | L   | Op-code   | MRS          | Mode Register<br>access                |       |

| Row active       | н   | Х    | Х    | Х   | Х         | DSEL         | NOP                                    |       |

|                  | L   | Н    | Н    | н   | Х         | NOP          | NOP                                    |       |

|                  | L   | Н    | L    | Н   | BA,CA,A10 | READ/READAP  | Begin read:<br>Optional AP             | 6     |

|                  | L   | Н    | L    | L   | BA,CA,A10 | WRIT/WRITEAP | Begin write:<br>Optional AP            | 6     |

|                  | L   | L    | Н    | Н   | BA,RA     | ACT          | ILLEGAL                                | 4     |

|                  | L   | L    | Н    | L   | BA,A10    | PRE/PALL     | Precharge                              | 7     |

|                  | L   | L    | L    | Н   | Х         | CBR/SELF     | ILLEGAL                                | 14    |

|                  | L   | L    | L    | L   | OP-code   | MRS          | ILLEGAL                                | 14    |

| READ             | н   | х    | Х    | х   | Х         | DSEL         | Continue burst to<br>end -> Row active |       |

|                  | L   | Н    | Н    | Н   | Х         | NOP          | Continue burst to<br>end -> Row active |       |

|                  | L   | Н    | L    | Н   | BA,CA,A10 | READ/READAP  | Term burst, new<br>read:Optional AP    | 8     |

|                  | L   | Н    | L    | L   | BA,CA,A10 | WRIT/WRITEAP | Term burst,start<br>write:Optional AP  | 8,9   |

|                  | L   | L    | Н    | Н   | BA,RA     | ACT          | ILLEGAL                                | 4     |

#### Table 8. Operative Command Table (Sheet 2 of 4)

| Current<br>state                | CS# | RAS# | CAS# | WE# | Address   | Command      | Action                                                                | Notes |

|---------------------------------|-----|------|------|-----|-----------|--------------|-----------------------------------------------------------------------|-------|

|                                 | L   | L    | н    | L   | BA,A10    | PRE/PALL     | Term<br>burst,precharge                                               |       |

|                                 | L   | L    | L    | н   | Х         | CBR/SELF     | ILLEGAL                                                               | 14    |

|                                 | L   | L    | L    | L   | Opcode    | MRS          | ILLEGAL                                                               | 14    |

| WRITE                           | н   | х    | х    | х   | х         | DSEL         | Continue burst to<br>end ->Write<br>recovering                        |       |

|                                 | L   | Н    | Н    | н   | х         | NOP          | Continue burst to<br>end -> Write<br>recovering                       |       |

|                                 | L   | Н    | L    | Н   | BA,CA,A10 | READ/READAP  | Term burst, start read: optional AP                                   | 8,9   |

|                                 | L   | Н    | L    | L   | BA,CA,A10 | WRIT/WRITEAP | Term burst, new<br>write: optional AP                                 | 8     |

|                                 | L   | L    | Н    | Н   | BA,RA     | ACT          | ILLEGAL                                                               | 4     |

|                                 | L   | L    | Н    | L   | BA,A10    | PRE/PALL     | Term burst<br>precharging                                             | 10    |

|                                 | L   | L    | L    | Н   | Х         | CBR/SELF     | ILLEGAL                                                               | 14    |

|                                 | L   | L    | L    | L   | Op Code   | MRS          | ILLEGAL                                                               | 14    |

| Read with<br>auto<br>precharge  | н   | х    | х    | х   | х         | DSEL         | Continue burst to<br>end -> precharging                               |       |

|                                 | L   | Н    | Н    | н   | Х         | NOP          | Continue burst to<br>end -> precharging                               |       |

|                                 | L   | Н    | L    | Н   | BA,CA,A10 | READ/READAP  | ILLEGAL                                                               | 13    |

|                                 | L   | Н    | L    | L   | BA,CA,A10 | WRIT/WRITEAP | ILLEGAL                                                               | 13    |

|                                 | L   | L    | Н    | Н   | BA,RA     | ACT          | ILLEGAL                                                               | 4,13  |

|                                 | L   | L    | Н    | L   | BA,A10    | PRE/PALL     | ILLEGAL                                                               | 4,13  |

|                                 | L   | L    | L    | Н   | Х         | CBR/SELF     | ILLEGAL                                                               | 14    |

|                                 | L   | L    | L    | L   | Opcode    | MRS          | ILLEGAL                                                               | 14    |

| Write with<br>auto<br>precharge | н   | х    | х    | х   | х         | DSEL         | Continue burst to<br>end ->Write<br>recovering with<br>auto precharge |       |

|                                 | L   | Н    | н    | н   | х         | NOP          | Continue bust to<br>end-> Write<br>recovering with<br>auto precharge  |       |

|                                 | L   | Н    | L    | Н   | BA,CA,A10 | READ/READAP  | ILLEGAL                                                               | 13    |

|                                 | L   | Н    | L    | L   | BA,CA,A10 | WRIT/WRITEAP | ILLEGAL                                                               | 13    |

|                                 | L   | L    | Н    | Н   | BA,RA     | ACT          | ILLEGAL                                                               | 4,13  |

|                                 | L   | L    | Н    | L   | BA,A10    | PRE/PALL     | ILLEGAL                                                               | 4,13  |

|                                 | L   | L    | L    | Н   | Х         | CBR/SELF     | ILLEGAL                                                               | 14    |

|                                 | L   | L    | L    | L   | Opcode    | MRS          | ILLEGAL                                                               | 14    |

| Current<br>state                              | CS# | RAS# | CAS# | WE# | Address   | Command          | Action                                 | Notes       |

|-----------------------------------------------|-----|------|------|-----|-----------|------------------|----------------------------------------|-------------|

| Prechargin<br>g                               | Н   | х    | х    | х   | х         | DSEL             | NOP- Enter Idle<br>after Trp           |             |

|                                               | L   | н    | н    | н   | Х         | NOP              | NOP-Enter Idle<br>after Trp            |             |

|                                               | L   | Н    | L    | Н   | BA,CA,A10 | READ/READAP      | ILLEGAL                                | 4,13        |

|                                               | L   | Н    | L    | L   | BA,CA,A10 | WRIT/WRITEAP     | ILLEGAL                                | 4,13        |

|                                               | L   | L    | Н    | Н   | BA,RA     | ACT              | ILLEGAL                                | 4,13        |

|                                               | L   | L    | Н    | L   | BA,A10    | PRE/PALL         | NOP- Enter Idle<br>after Trp           |             |

|                                               | L   | L    | L    | Н   | Х         | CBR/SELF         | ILLEGAL                                | 14          |

|                                               | L   | L    | L    | L   | Op Code   | MRS              | ILLEGAL                                | 14          |

| Row activating                                | н   | х    | Х    | х   | Х         | DSEL             | NOP- Enter row<br>active after Trcd    |             |

|                                               | L   | Н    | Н    | н   | Х         | NOP              | NOP- Enter row<br>active after Trcd    |             |

|                                               | L   | Н    | L    | Н   | BA,CA,A10 | READ/ READAP     | ILLEGAL                                | 4,13        |

|                                               | L   | Н    | L    | L   | BA,CA,A10 | WRIT/<br>WRITEAP | ILLEGAL                                | 4,13        |

|                                               | L   | L    | Н    | н   | BA,RA     | ACT              | ILLEGAL                                | 4,11,1<br>3 |

|                                               | L   | L    | Н    | L   | BA,A10    | PRE/PALL         | ILLEGAL                                | 4,13        |

|                                               | L   | L    | L    | Н   | Х         | CBR/SELF         | ILLEGAL                                | 14          |

|                                               | L   | L    | L    | L   | Opcode    | MRS              | ILLEGAL                                | 14          |

| Write<br>Recovering                           | н   | х    | Х    | х   | Х         | DSEL             | NOP - Enter row<br>active after Tdpl   |             |

|                                               | L   | н    | Н    | н   | Х         | NOP              | NOP - Enter row<br>active after Tdpl   |             |

|                                               | L   | н    | L    | н   | BA,CA,A10 | READ/ READAP     | Start Read,<br>optional AP             | 9           |

|                                               | L   | Н    | L    | L   | BA,CA,A10 | WRIT/<br>WRITEAP | New Write,<br>optional AP              |             |

|                                               | L   | L    | Н    | Н   | BA,RA     | ACT              | ILLEGAL                                | 4,13        |

|                                               | L   | L    | Н    | L   | BA,A10    | PRE/PALL         | ILLEGAL                                | 4,14        |

|                                               | L   | L    | L    | Н   | Х         | CBR/SELF         | ILLEGAL                                | 14          |

|                                               | L   | L    | L    | L   | Opcode    | MRS              | ILLEGAL                                | 14          |

| Write<br>recovering<br>with auto<br>precharge | Н   | x    | х    | х   | Х         | DSEL             | NOP - Enter<br>precharge after<br>Tdpl |             |

|                                               | L   | Н    | Н    | н   | х         | NOP              | NOP - Enter<br>precharge after<br>Tdpl |             |

|                                               | L   | н    | L    | Н   | BA,CA,A10 | READ/ READAP     | ILLEGAL                                | 4,9,13      |

| Table 8. | Operative | Command | Table | (Sheet 4 of 4) |

|----------|-----------|---------|-------|----------------|

|----------|-----------|---------|-------|----------------|

| Current<br>state              | CS# | RAS# | CAS# | WE# | Address   | Command                            | Action                         | Notes |

|-------------------------------|-----|------|------|-----|-----------|------------------------------------|--------------------------------|-------|

|                               | L   | н    | L    | L   | BA,CA,A10 | WRIT/<br>WRITEAP                   | ILLEGAL                        | 4,13  |

|                               | L   | L    | Н    | Н   | BA,RA     | ACT                                | ILLEGAL                        | 4,13  |

|                               | L   | L    | Н    | L   | BA,A10    | PRE/PALL                           | ILLEGAL                        | 4,14  |

|                               | L   | L    | L    | Н   | Х         | CBR/SELF                           | ILLEGAL                        | 14    |

|                               | L   | L    | L    | L   | Op Code   | MRS                                | ILLEGAL                        | 14    |

| Refreshing                    | н   | х    | х    | х   | Х         | DSEL                               | NOP - Enter idle after trc     |       |

|                               | L   | н    | Н    | н   | Х         | NOP                                | NOP- Enter idle after trc      |       |

|                               | L   | н    | L    | Х   | Х         | READ/ READAP                       | ILLEGAL                        | 14    |

|                               | L   | L    | Н    | Х   | Х         | ACT/PRE/PALL                       | ILLEGAL                        | 14    |

|                               | L   | L    | L    | Х   | Х         | CBR/SELF/MRS                       | ILLEGAL                        | 14    |

| Mode<br>Register<br>accessing | н   | х    | х    | х   | х         | DSEL                               | NOP - Enter idle<br>after tmrd |       |

|                               | L   | н    | н    | н   | х         | NOP                                | NOP - Enter idle after tmrd    |       |

|                               | L   | Н    | L    | х   | х         | READ/ WRITE/<br>READAP/<br>WRITEAP | ILLEGAL                        | 14    |

|                               | L   | L    | х    | х   | х         | ACT/PRE/<br>PALL/ CBR/<br>SELF/MRS | ILLEGAL                        | 14    |

#### NOTES:

- 1. H: High Level, L: Low Level, X: don't care, V: Valid data input, BA: Bank Address, AP: (Auto Precharge), CA: (Column Address), RA: (Row Address)

- 2. All entries assume that CKE was active (high level) during the preceding clock cycle.

- 3. If both banks are idle and CKE is inactive (low level), then in power down mode.

- 4. Illegal to bank in specified states. Function may be legal in the bank indicated by Bank Address (BA), depending on the state of that bank.

- 5. If both banks are idle and CKE is inactive (low level), then Self refresh mode.

- 6. Illegal if trcd is not satisfied.

- 7. Illegal if tras is not satisfied.

- 8. Must satisfy burst interupt condition.

- 9. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

- 10.Must mask preceding data which don't satisfy tdpl.

- 11. Illegal if trrd is not satisfied.

- 12.Burst Stop command is disabled.

- 13. llegal for single bank, but legal for other banks in multi-bank devices.

- 14.Illegal for all banks.

| Memory Size | # Banks | # Bank<br>Addresses | # Row<br>Addresses | # Column<br>Addresses |

|-------------|---------|---------------------|--------------------|-----------------------|

| 16M 2 bank  |         |                     | I I                |                       |

| 1Mx16       | 2       | 1                   | 11                 | 8                     |

| 2Mx8        | 2       | 1                   | 11                 | 9                     |

| 4Mx4        | 2       | 1                   | 11                 | 10                    |

| 64M 4 bank  |         | •                   | · · ·              |                       |

| 2Mx32       | 4       | 2                   | 11                 | 8                     |

| 4Mx16       | 4       | 2                   | 12                 | 8                     |

| 8Mx8        | 4       | 2                   | 12                 | 9                     |

| 16Mx4       | 4       | 2                   | 12                 | 10                    |

| 128M 4 bank |         | •                   | · · ·              |                       |

| 4Mx32       | 4       | 2                   | 12                 | 8                     |

| 8Mx16       | 4       | 2                   | 12                 | 9                     |

| 16Mx8       | 4       | 2                   | 12                 | 10                    |

| 32Mx4       | 4       | 2                   | 12                 | 11                    |

| 256M 4 bank |         | •                   |                    |                       |

| 8Mx32       | 4       | 2                   | 13                 | 8                     |

| 16Mx16      | 4       | 2                   | 13                 | 9                     |

| 32Mx8       | 4       | 2                   | 13                 | 10                    |

| 64Mx4       | 4       | 2                   | 13                 | 11                    |

#### Table 9. Row/Column Addresssing Per Memory Size/# Banks

#### 3.3 Address Bit Maps

#### 3.3.1 16M Address Bit Maps For Row And Column Addresses During Commands

#### Table 10. Row Address Table (ACT, PRE)

| Address Bit | Value | Command Type                   | Function                  | Memory Organization |

|-------------|-------|--------------------------------|---------------------------|---------------------|

| A11         | 0     | Row Activate (ACT), PRE,       | Bank0 Activate/ Precharge | 1Mx16, 2Mx8, 4Mx4   |

| A11         | 1     | Row Activate (ACT), PRE        | Bank1 Activate/ Precharge | 1Mx16, 2Mx8, 4Mx4   |

| A10         | 0,1   | Row Activate (ACT)             | Row address               | 1Mx16, 2Mx8, 4Mx4   |

| A10         | 0     | Precharge Single Bank<br>(PRE) | Precharge Selected Bank   | 1Mx16, 2Mx8, 4Mx4   |

| A10         | 1     | Precharge All Banks (PALL)     | Precharge All Banks       | 1Mx16, 2Mx8, 4Mx4   |

| A9-A0       | V     | Row Activate (ACT)             | Row Address               | 1Mx16, 2Mx8, 4Mx4   |

#### Table 11. Column Address Table (Read/Write/Read AP/Write AP)

| Address Bit | Value | Command Type             | Function                                 | Memory Organization |

|-------------|-------|--------------------------|------------------------------------------|---------------------|

| A11         | 0     | Read(READ), Write(WRITE) | Bank0 Read/Write                         | 1Mx16, 2Mx8, 4Mx4   |

| A11         | 1     | Read(READ), Write(WRITE) | Bank1 Read/Write                         | 1Mx16, 2Mx8, 4Mx4   |

| A10         | 0     | Read(READ), Write(WRITE) | Disable Auto Precharge<br>during Command | 1Mx16, 2Mx8, 4Mx4   |

| A10         | 1     | Read(READ), Write(WRITE) | Enable Auto Precharge<br>during Command  | 1Mx16, 2Mx8, 4Mx4   |

| A9          | V     | Read(READ), Write(WRITE) | Column Address                           | 4Mx4                |

| A9          | Х     | Read(READ), Write(WRITE) | None                                     | 1Mx16, 2Mx8         |

| A8          | V     | Read(READ), Write(WRITE) | Column Address                           | 4Mx4, 2Mx8          |

| A8          | Х     | Read(READ), Write(WRITE) | None                                     | 1Mx16               |

| A0-A7       | V     | Read(READ), Write(WRITE) | Column Address                           | 1Mx16, 2Mx8, 4Mx4   |

### 3.3.2 64M Address Bit Maps For Row And Column Addresses During Commands

| Address Bit | Value | Command Type                   | Function                  | Memory Organization |

|-------------|-------|--------------------------------|---------------------------|---------------------|

| BA0         | 0,1   | Bank Select                    | Bank0/1 (2 bank device)   | x4,x8,x16,x32       |

| BA1         | 0,1   | Bank Select                    | Bank2/3 (4 bank device)   | x4,x8,x16,x32       |

| A12         | V     | Row Activate (ACT)             | Row Address (2 bank only) | x4,x8,x16           |

| A11         | V     | Row Activate (ACT)             | Row Address               | x32 (2 bank only)   |

| A11         | V     | Row Activate (ACT)             | Row Address               | x4,x8,x16           |

| A10         | V     | Row Activate (ACT)             | Row Address               | x4,x8,x16,x32       |

| A10         | 0     | Precharge Single Bank<br>(PRE) | PREcharge Selected Bank   | x4,x8,x16,x32       |

| A10         | 1     | Precharge All Banks (PALL)     | PREcharge All Banks       | x4,x8,x16,x32       |

| A9-A0       | V     | Row Activate (ACT)             | Row Address               | x4,x8,x16,x32       |

#### Table 12. Row Address Table (ACT, PRE) (per JEDEC Standard)

#### Table 13. Column Address Table (Read/Write/Read AP/Write AP)

| Address Bit | Value | Command Type             | Function                                 | Memory Organization |

|-------------|-------|--------------------------|------------------------------------------|---------------------|

| BA0         | 0,1   | Bank Select              | Bank0/1 (2 bank device)                  | x4,x8,x16,x32       |

| BA1         | 0,1   | Bank Select              | Bank2/3 (4 bank device)                  | x4,x8,x16,x32       |

| A10         | 0     | Read(READ), Write(WRITE) | Disable Auto Precharge<br>during Command | x4,x8.x16,x32       |

| A10         | 1     | Read(READ), Write(WRITE) | Enable Auto Precharge<br>during Command  | x4,x8,x16,x32       |

| A9          | V     | Read(READ), Write(WRITE) | Column Address                           | x4                  |

| A9          | Х     | Read(READ), Write(WRITE) | None                                     | x8,x16,x32          |

| A8          | V     | Read(READ), Write(WRITE) | Column Address                           | x4,x8               |

| A8          | Х     | Read(READ), Write(WRITE) | None                                     | x16,x32             |

| A0-A7       | V     | Read(READ), Write(WRITE) | Column Address                           | x4,x8,x16,x32       |

#### 3.3.3 128M Address Bit Maps For Row And Column Addresses During Commands

#### Table 14. Row Address Table (ACT, PRE)

| Address Bit | Value | Command Type                   | Function                   | Memory Organization |

|-------------|-------|--------------------------------|----------------------------|---------------------|

| BA0         | 0,1   | Bank Select                    | Bank0/1 (2 bank device)    | x4,x8,x16,x32       |

| BA1         | 0,1   | Bank Select                    | Bank2/3 (4 bank device)    | x4,x8,x16,x32       |

| A11         | V     | Row Activate (ACT)             | Row Address                | x4,x8,x16,x32       |

| A10         | V     | Row Activate (ACT)             | Row Address                | x4,x8,x16,x32       |

| A10         | 0     | Precharge Single Bank<br>(PRE) | PREcharge Selected<br>Bank | x4,x8,x16,x32       |

| A10         | 1     | Precharge All Banks (PALL)     | PREcharge All Banks        | x4,x8,x16,x32       |

| A9-A0       | V     | Row Activate (ACT)             | Row Address                | x4,x8,x16,x32       |

#### Table 15. Column Address Table (Read/Write/Read AP/Write AP)

| Address Bit | Value | Command Type             | Function                              | Memory Organization |

|-------------|-------|--------------------------|---------------------------------------|---------------------|

| BA0         | 0,1   | Bank Select              | Bank0/1 (2 bank device)               | x4,x8,x16,x32       |

| BA1         | 0,1   | Bank Select              | Bank2/3 (4 bank device)               | x4,x8,x16,x32       |

| A11         | Х     | Read(READ), Write(WRITE) | None                                  | x8,x16,x32          |

| A11         | V     | Read(READ), Write(WRITE) | Column Address                        | x4                  |

| A10         | 0     | Read(READ), Write(WRITE) | Disable Auto Precharge during Command | x4,x8,x16,x32       |

| A10         | 1     | Read(READ), Write(WRITE) | Enable Auto Precharge during Command  | x4,x8,x16,x32       |

| A9          | V     | Read(READ), Write(WRITE) | Column Address                        | x4,x8               |

| A9          | Х     | Read(READ), Write(WRITE) | None                                  | x16,x32             |

| A8          | V     | Read(READ), Write(WRITE) | Column Address                        | x4,x8,x16           |

| A8          | Х     | Read(READ), Write(WRITE) | None                                  | x32                 |

| A0-A7       | V     | Read(READ), Write(WRITE) | Column Address                        | x4,x8,x16,x32       |

#### 3.3.4 256M Address Bit Maps For Row And Column Addresses During Commands

#### Table 16. Row Address Table (ACT, PRE)

| Address Bit | Value | Command Type                   | Function                   | Memory Organization |

|-------------|-------|--------------------------------|----------------------------|---------------------|

| BA0         | 0,1   | Bank Select                    | Bank0/1 (2 bank device)    | x4,x8,x16,x32       |

| BA1         | 0,1   | Bank Select                    | Bank2/3 (4 bank device)    | x4,x8,x16,x32       |

| A12         | V     | Row Activate (ACT)             | Row Address                | x4,x8,x16,x32       |

| A11         | V     | Row Activate (ACT)             | Row Address                | x4,x8,x16,x32       |

| A10         | V     | Row Activate (ACT)             | Row Address                | x4,x8,x16,x32       |

| A10         | 0     | Precharge Single Bank<br>(PRE) | PREcharge Selected<br>Bank | x4,x8,x16,x32       |

| A10         | 1     | Precharge All Banks (PALL)     | PREcharge All Banks        | x4,x8,x16,x32       |

| A9-A0       | V     | Row Activate (ACT)             | Row Address                | x4,x8,x16,x32       |

#### Table 17. Column Address Table (Read/Write/Read AP/Write AP)

| Address Bit | Value | Command Type             | Function                                 | Memory Organization |

|-------------|-------|--------------------------|------------------------------------------|---------------------|

| BA0         | 0,1   | Bank Select              | Bank0/1 (2 bank device)                  | x4,x8,x16,x32       |

| BA1         | 0,1   | Bank Select              | Bank2/3 (4 bank device)                  | x4,x8,x16,x32       |

| A11         | Х     | Read(READ), Write(WRITE) | None                                     | x8,x16,x32          |

| A11         | V     | Read(READ), Write(WRITE) | Column Address                           | x4                  |

| A10         | 0     | Read(READ), Write(WRITE) | Disable Auto Precharge<br>during Command | x4,x8.x16,x32       |

| A10         | 1     | Read(READ), Write(WRITE) | Enable Auto Precharge during command     | x4,x8.x16,x32       |

| A9          | V     | Read(READ), Write(WRITE) | Column Address                           | x4,x8               |

| A9          | Х     | Read(READ), Write(WRITE) | None                                     | x16,x32             |

| A8          | V     | Read(READ), Write(WRITE) | Column Address                           | x4,x8,x16           |

| A8          | Х     | Read(READ), Write(WRITE) | None                                     | x32                 |

| A0-A7       | V     | Read(READ), Write(WRITE) | Column Address                           | x4,x8,x16,x32       |

#### 3.4 **Power-Up and Initialization Sequence**

#### 3.4.1 Power Up Sequence

The SDRAM should be initialized by the following sequence of operations:

- 1. Clock will be applied at power up along with power (clock frequency will be unknown).

- 2. The clock will stabilize within 100usec before the first command to SDRAM is attempted.

- 3. All the control inputs, RAS#, CAS#, WE#, CS# will be held in an undefined state (either valid high or low) during reset. After reset is complete CS# will be held inactive before the first access to SDRAM is attempted. All other address and control signals will be driven to a valid state.

4. The levels on all the address inputs should be ignored. (All the address inputs can be indeterminate.)

#### 3.4.2 Initialization Sequence

The initialization sequence can be issued at *anytime*. Following the initialization sequence, the device must be ready for full functionality. SDRAM devices are initialized by the following sequence:

- 1. At least one NOP cycle will be issued after the 1msec device deselect.

- 2. A minimum pause of 200usec will be provided after the NOP.

- 3. A precharge all (PALL) will be issued to the SDRAM.

- 4. 8 Auto refresh (CBR) refresh cycles will be provided.

- 5. A mode register set (MRS) cycle will be issued to program the SDRAM parameters (e.g., Burst length, CAS# latency etc.).

- 6. After MRS the device should be ready for full functionality within 3 clocks after  $T_{mrd}$  is met.

#### Figure 5. Power Up Initialization Sequence

#### 3.5 Precharge Selected Bank

The precharge operation should be performed on the active bank when precharge selected bank command is issued. When the precharge command is issued with address A10 low, A11 selects the bank to be precharged. At the end of the precharge selected bank command the selected bank should be in idle state after the minimum  $t_{RP}$  is met.

#### 3.6 Precharge All

All the banks should be precharged at the same time when this command is issued. When the precharge command is issued with address  $A_{10}$  high then all the banks will be precharged. At the end of the precharge all command all the banks should be in idle state after the minimum  $t_{RP}$  is met.

| A10  | A11  | 16M 2 Bank Precharge (type) |

|------|------|-----------------------------|

| Low  | Low  | Precharge bank 0            |

| Low  | High | Precharge bank 1            |

| High | Х    | Precharge All banks         |

| A10  | A12  | A13  | 64M/128M/256M 4 Bank<br>Precharge (type) |

|------|------|------|------------------------------------------|

| Low  | Low  | Low  | Precharge Bank 0                         |

| Low  | High | Low  | Precharge Bank 1                         |

| Low  | Low  | High | Precharge Bank 2                         |

| Low  | High | High | Precharge Bank 3                         |

| High | Х    | Х    | Precharge All Banks                      |

#### 3.7 NOP and Device Deselect

The device should be deselected by deactivating the CS# signal. In this mode SDRAM should ignore all the control inputs. The SDRAMs are put in NOP mode when CS# is active and by deactivating RAS#, CAS# and WE#. For both Deselect and NOP the device should finish the current operation when this command is issued.

#### **3.8** Row activate

This command selects a row in a specified bank of the device. Read and write operations can only be initiated on this activated bank after the minimum  $t_{RCD}$  time is elapsed from the activate command.

#### 3.9 Read Bank

This command is used after the row activate command to initiate the burst read of data. The read command is initiated by activating CS#, CAS# and deasserting WE# at the same clock sampling (rising) edge as described in the command truth table. The length of the burst and the CAS# latency time will be determined by the values programmed during the MRS command.

#### 3.10 Write Bank

This command is used after the row activate command to initiate the burst write of data. The write command is initiated by activating CS#, CAS# and WE# at the same clock sampling (rising) edge as described in the command truth table. The length of the burst will be determined by the values programmed during the MRS command.

#### 3.11 Mode Register Set Command